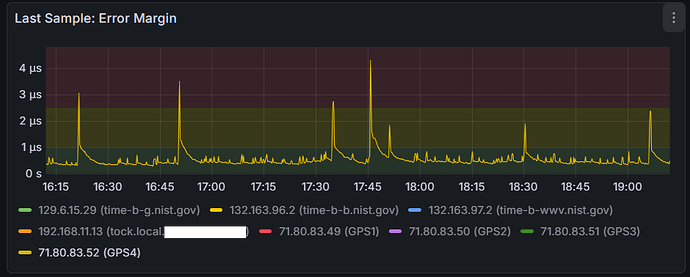

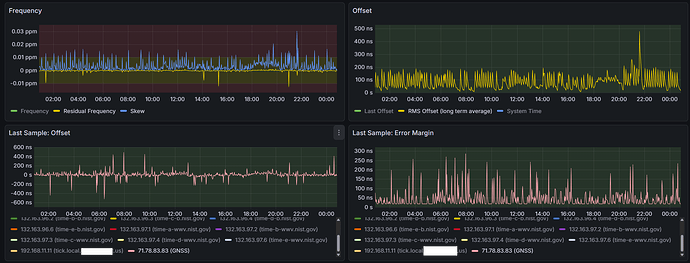

Here are some snips of the last couple days of testing at polling interval 10 (1024 s)

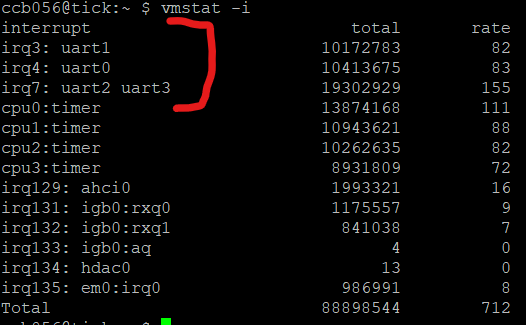

Before this I did some preliminary testing, moved GPS receivers between COM ports to see if the behavior was due to the GPS receivers or the COM ports, and I’ve convinced myself the discrepancies are 100% with the COM ports, not the receivers - essentially the COM ports with software timestamping have a precision on microsecond scale and each COM port is different, where the LEA-M8T’s are nanosecond scale precision (as tested on Raspberry Pi 5 with satpulse, chrony, and hardware timestamping to PHC)

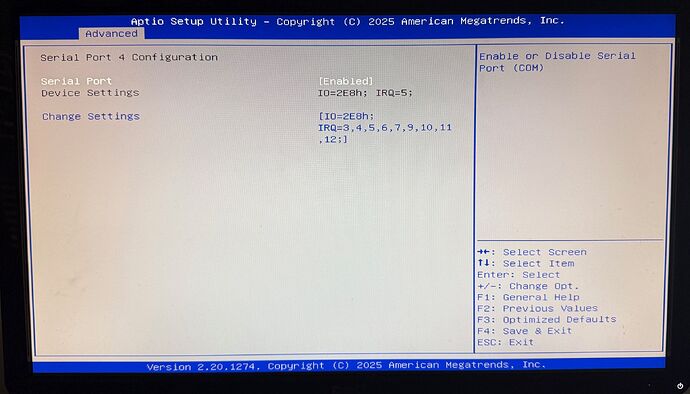

GPS1-3 set to noselect, using only GPS4 (COM 4, even with IRQ sharing with COM 3, has much better precision than the others)

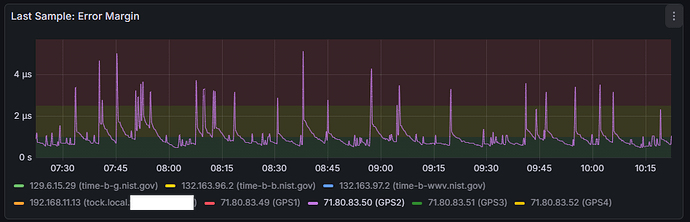

As shown in the Error Margin graph, COM1 (red) hangs out around 2us precision, COM2 (purple) sticks around 200 ns and occasionally spikes to over 1 us, COM3 (green) is all over the place between 2 us and 150 ns, and COM4 (yellow) holds steady around 500 ns.

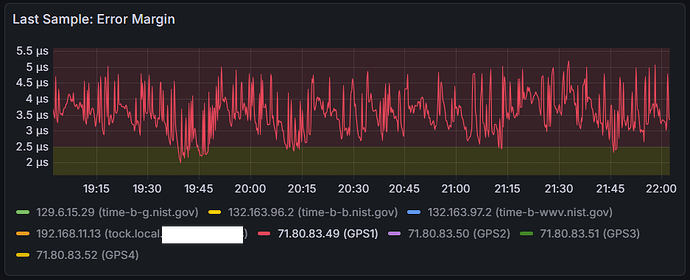

But I need to fix this problem with the offsets caused by the COM ports:

These lines need to be on top of each other, not spaced 10’s of us apart…

Otherwise when chrony decides to change refclocks, the RMS offset will spike

So, I looked at a few areas where the error margins for COMs 2-4 were all low at the same time, and recorded their offsets - and then tweaked the offset directives in the chrony config file.

Since GPS3 was always the lowest offset, I’m adjusting the others down the GPS3 - but its anyone’s guess where the exact second is, best I can do is bring the sources I have into alignment - COM1 is adjusted by 13 us, COMs 2 and 4 between 30-40 us.

Also added precision directives to each refclock to account for the error margin I’m seeing

Resetting the refclocks back to their default polling interval, and removing the noselects, will see how this goes…

refclock SOCK /var/run/chrony.cuau0.sock refid GPS1 offset +0.0000137 precision 2e-6

refclock SOCK /var/run/chrony.cuau1.sock refid GPS2 offset -0.0999666 precision 1e-6

refclock SOCK /var/run/chrony.cuau2.sock refid GPS3 offset -0.2000000 precision 2e-6

refclock SOCK /var/run/chrony.cuau3.sock refid GPS4 offset -0.2999625 precision 0.5e-6